HART: A Hybrid Architecture for Ray Tracing Animated Scenes

Jae-Ho

Nah1,3,4, Jin-Woo

Kim1, Junho Park1, Won-Jong Lee2,

Jeong-Soo Park2, Seok-Yoon Jung2,

Woo-Chan Park3,

Dinesh Manocha4,

and Tack-Don Han1

1Yonsei University, 2Samsung

Electronics, 3Sejong University, 4University

of North Carolina at Chapel Hill

![]()

|

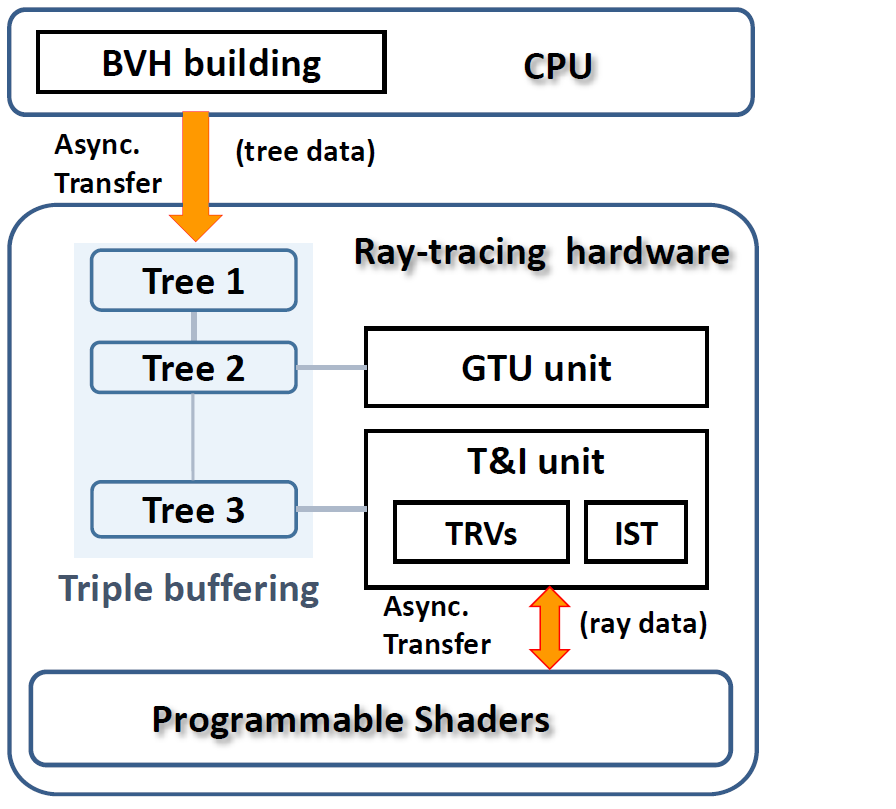

We present a hybrid architecture, inspired by

asynchronous BVH construction, for ray tracing

animated scenes. Our hybrid architecture utilizes

heterogeneous hardware resources: dedicated

ray-tracing hardware for BVH updates and ray traversal

and a CPU for BVH reconstruction. We also present a

traversal scheme using a primitive’s axis-aligned

bounding box (PrimAABB). This scheme reduces

ray-primitive intersection tests by reusing existing

BVH traversal units and the primAABB data for tree

updates; it enables the use of shallow trees to reduce

tree build times, tree sizes, and bus bandwidth

requirements. Furthermore, we present a cache scheme

that exploits consecutive memory access by reusing

data in an L1 cache block. We perform cycle-accurate

simulations to verify our architecture, and the

simulation results indicate that the proposed

architecture can achieve real-time Whitted ray tracing

animated scenes at 1920x1200 resolution. This result

comes from our high-performance hardware architecture

and minimized resource requirements for tree updates. |

[Teaser Image]

[Publication]

- IEEE Transactions on Visualization and Computer Graphics,

preprint [pdf]